Friday, January 13, 2017

Core 14. x div a

We can find the x div a macro in Library -> Math Mod -> x div a.

While the / module will divide at once, the x div a macro will wait until x changes.

This is shown by comparing the two. The two output only match when x changes. Thus when a is changing, only the / output changes.

The core cell structure:

The primary structure:

The panel view showing a changing leading to difference in outputs:

Core 13. x mul a

We can find the x mul a macro in Library -> Math Mod -> x mul a.

While the * module will multiply at once, the x mul a will wait until x changes.

This is shown by comparing the two. The two output only match when x changes. Thus when a is changing, only the * output changes.

The core cell structure:

The primary structure:

The panel view showing a changing leading to difference in outputs:

Thursday, January 12, 2017

Core 12. Sine oscillator

The last example provides the argument for different oscillators.

Here we will drive it through a sine macro, which is available from Library -> Math -> Trig-Hyp -> sin.

The sine macro is added to the end, before the Out output port. You can double click the sine macro to see the structure, and keep on double clicking any nested macros.

The Core Cell structure:

The primary structure view showing now the scope is from -1 to +1:

The panel view:

Core 11. -pi to +pi oscillator

The last example was bound by 1. Now this example is bound by pi. However the lower value is not zero, but -pi.

We create 2 QuickBuses, with a value of pi and 2*pi.

Note that we have added a * module near the Freq input with a value of 2*pi. In the last example the range was 1, thus it was same as multiplication by 1. However now the range is 2*pi, and thus we have to multiply with this value, so the time period is consistent.

We use a Compare module to see if the latch value is above pi. If it is, it will be subtracted by 2*pi to go back to minus pi.

The Core Cell view:

The primary structure view with a scope from -pi to pi over 1 millisecond:

The Panel view:

Core 10. Ramp oscillator

In the last example the output kept on increasing. Here the upper bound is 1.

The output starts at zero, and at each sampling rate clock, increases by Freq/SR, where SR is usually 44100.

A Compare module will see if it is above 1. If so, it will go to the upper router output and have a value of 1 subtracted, thus it should be back at 0.

The counter value from the two cases (either less than 1 or subtracted by 1) are merged and fed into the Write module.

Thus the value from the merge is always a value between 0 and 1.

In the primary structure, we connect the Core Cell output to a Scope. The Scope will show a 1 millisecond signal from -1 to +1.

The core cell structure:

The primary structure:

The panel view:

Core 9. Using Sample Rate Clock of Standard Distribution

Now we do not use a Clock oscillator from the primary structure.

Instead we use the sample rate clock (right-click on clock terminal and select Pickup Standard Distribution Bus, and then Pickup SR.C).

Since the sample rate clock increases ticks 44100 times per second, we have to have to add 1 divided by 44100 each time. Thus now the output will be in seconds. If the Freq is 2, rather than 1, it will increase twice as fast and so on. We can get the sample rate as SR.R from the Std. Distribution Bus. Usually the Sample Rate will be 44100.

We also have changed the output Cnt as Audio rate signal rather than control rate using the Properties Sidebar.

The Core Cell structure:

The primary structure view:

The panel view:

Core 8. Reset using Write module

This example is similar to the previous example except for the Reset signal.

The Reset signal goes to a Write module. Thus whenever it is activated, it will write a value of zero to the latch.

The Core Cell view:

The primary structure view:

The Panel view:

Core 7. Reset of Counter using Merge

A Clock Oscillator with a Frequency F is connected to Inc input of the Core Cell.

For the Core Cell, Inc is the clock to start Read operation sending latch value to + module which adds 1. Thus we add 1 each time we have an event.

The + module output is merged with the Reset signal, and sent to Write.

The Reset signal is a button, in the primary structure. The On and Off values both are 0, so a 0 event is sent whenever Reset button is clicked.

A knob Freq has properties Min of 1, Max of 10, and Step Size of 1. We divide Freq by 2 so the number of events is at a rate of Freq.

The Cnt value of the Core Cell is read by a Numeric Readout.

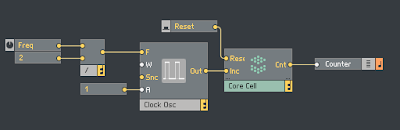

The core cell structure:

The primary structure:

The panel view:

Core 6. Accumulator

An input Inc goes to a Read module. If a clock is connected to Inc, it will generate Read requests periodically resulting in a counter. However, in the primary view, we will connect it to a button. Thus it will just serve as an Accumulator of click events on the button.

Each time the button is clicked, it will send its value to the Cnt output as well as a + module.

The + module will add 0.5 each time. In the default case, there are two events when a button is turned on and turned off. Thus each time, button is on, the Counter value (Cnt) will increase by 1. This is written back into the latch as well as sent out to a Numeric Readout in the primary structure.

The core cell:

The primary structure view (with input a button and output connected to a Numeric Readout):

The panel view:

Core 5. Samples per Beat using * and / modules

The multiplication and division modules are used to find the beats per second and samples per beat.

The Tempo Info primary module is used to give the tempo to the T input of the Core Cell. It gives the number of beats in one second. We set the project tempo to 240, so this will be 4.

In the core cell we get the reciprocal from the / module, which is the time in seconds of one beat (0.25 here). This time is multiplied by the sampling rate (which we can get by right-clicking on input terminal of the * module and selecting SR.R Pickup from the Standard Distribution Bus). The sampling rate is usually 44100 samples per second, thus we should get 1/4 of this number.

The beats per minute is just 60 times the beats per second, the T input value.

The Core cell view:

The primary structure view:

The Panel view:

Core 4. Read and Write modules

From Built-In-Modules -> Memory, we can find Write and Read latches.

We can send a value into the Write latch. Here we use a knob, named In, to set a value.

The Read latch will write out the value of the latch pair. A numeric readout will read the output value.

Internally, the latch must be connected with its OBC memory connections, which can be found at the bottom of the Read and Write modules.

However the read is only done when the Read latch receives a clock signal. Instead of using a clock, we will use a button, which sends events when its value changes.

Thus the In value is read out, by the numeric readout, when the button is clicked.

The core cell structure:

The primary structure:

The panel view (showing the Out and In will be same when button clicked):

Wednesday, January 11, 2017

Core 3. QuickBus

We can create wireless connections using QuickBuses.

For a + module, right-click on the inputs and connect to New QuickBus for the two of them. Name them A and B. Do the same for output, and name it sum.

Create 2 inputs (right-clicking in input area and selecting New -> In). Then right click on terminal and select Connect to QuickBus, select either A (top) or B (bottom).

Create output port (right-clicking in output area and selecting New -> Out). Right click on the terminal and connect it to QuickBus sum.

The core cell:

The primary structure view (with inputs connected to knobs with range from 0 to 5 in steps of 1 and output connected to a Numeric readout):

The panel view:

Core 2. Const module

This example is similar to last example, except now 2 Constant Modules are used, instead of QuickConsts.

Now to input of + module , we add two Const modules:

Built-in-module -> Const.

The Core cell view.

The primary structure view and the panel view is the same as in last example.

Core 1. QuickConst

To create a new Core Cell, right click in primary structure view, and select new Core Cell.

Double click it to enter the core structure.

Right click in normal area (the wide area between input and output

area), and select

Built-In-Modules -> Math -> +.

Right click on the inputs and select Connect to NewConst, and change numbers to 2 and 3.

Right-click on the output area, create a port and name it sum, and wire it to the output to adder.

The core cell structure:

The primary structure (with a Numeric to display the output from the sum):

The panel view:

Sunday, January 1, 2017

76. Event Table

An Event Table module can hold data.

In the Properties for the event table we set the size as 16 by 1. The range is -1 to 1 in steps of 0.1.

In the Panel view we right-click and select Draw Mode and then draw a shape.

The Sync Pls. clock is set at 1/16. Since beat is half a second for BPM of 120, the clock ticks 1/8 second. Since their are 16 values held by table, thus the period is 2 seconds.

The Scope buffer in Function tab should be 2000 ms.

This is the structure view:

This is the panel view:

This is the Audio view:

Subscribe to:

Comments (Atom)